# HfO<sub>x</sub>-Based Vertical Resistive Switching Random Access Memory Suitable for Bit-Cost-Effective Three-Dimensional Cross-Point Architecture

Shimeng Yu,<sup>†,\*</sup> Hong-Yu Chen,<sup>†</sup> Bin Gao,<sup>‡</sup> Jinfeng Kang,<sup>‡</sup> and H.-S. Philip Wong<sup>†,\*</sup>

<sup>†</sup>Department of Electrical Engineering and Center for Integrated Systems, Stanford University, California 94305, United States and <sup>‡</sup>Institute of Microelectronics, Peking University, Beijing, 100871, China

**ABSTRACT** The three-dimensional (3D) cross-point array architecture is attractive for future ultra-high-density nonvolatile memory application. A bit-cost-effective technology path toward the 3D integration that requires only one critical lithography step or mask for reducing the bit-cost is demonstrated in this work. A double-layer Hf0<sub>x</sub>-based vertical resistive switching random access memory (RRAM) is fabricated and characterized. The Hf0<sub>x</sub> thin film is deposited at the sidewall of the predefined trench by atomic layer deposition, forming a vertical memory structure. Electrode/oxide interface engineering with a TiON interfacial layer results in nonlinear *I*−*V* suitable for the selectorless array. The fabricated Hf0<sub>x</sub> vertical RRAM shows excellent performances such as reset current (<50  $\mu$ A), switching speed (<100 ns), switching endurance (>10<sup>8</sup> cycles), read disturbance immunity (>10<sup>9</sup> cycles), and data retention time (>10<sup>5</sup> s @ 125 °C).

**KEYWORDS:** resistive switching  $\cdot$  RRAM  $\cdot$  cross-point array  $\cdot$  HfO<sub>2</sub>  $\cdot$  bit-cost-effective  $\cdot$  3D integration

esistive switching random access memory (RRAM) is one of the most Npromising candidates for future nonvolatile memory application.<sup>1,2</sup> The electrically triggered resistance switching phenomenon has been observed in dozens of materials, including amorphous silicon,<sup>3</sup> amorphous carbon,<sup>4</sup> chalcogenide,<sup>5</sup> and oxides such as NiO,<sup>6</sup> TiO<sub>x</sub>,<sup>7</sup> WO<sub>x</sub>,<sup>8</sup> HfO<sub>x</sub>,<sup>9,10</sup> TaO<sub>x</sub>,<sup>11</sup> and AlO<sub>x</sub>.<sup>12</sup> Among these materials, the oxide-based RRAM has shown attractive performances including fast switching speed ( $\sim$ ns<sup>9</sup>), excellent scalability (<10 nm cell size<sup>10</sup>), long endurance (>10<sup>12</sup> cycles<sup>11</sup>), and stable data retention at elevated temperature (>10 years extrapolated $^{9-11}$ ), along with compatibility with the complementary metal-oxidesemiconductor (CMOS) technology. In addition, Mb-size array with CMOS peripheral circuits has been demonstrated in HfOx RRAM.<sup>13</sup> However, the RRAM technology has not yet begun to replace the mainstream commercialized FLASH technology even though RRAM has shown better switching speed and endurance than FLASH technology.

In addition to the challenges from device physics such as variability control,<sup>14</sup> a key challenge for RRAM is improving the integration density in terms of cost per bit (bit-cost), so it can compete with the multibit storage NAND FLASH. State-of-the-art NAND FLASH has been scaled down to the sub-20 nm regime,<sup>15</sup> and the three-dimensional (3D) stackable NAND FLASH is emerging.<sup>16–19</sup> To achieve similar device density to the 3D NAND FLASH, a technology path toward the 3D stackable RRAM is required. There are two 3D integration approaches available: one is the conventional planar RRAM-based cross-point array<sup>20,21</sup> stacked layer by layer; the other one is the novel vertical RRAM<sup>22,23</sup> sandwiched between the pillar electrodes and multilayer plane electrodes. The first approach using simply stacked planar RRAM does not save lithography steps or masks, and therefore the bit-cost remains high. The second approach, using vertical RRAM, requires only one critical lithography step or mask; thus it is a more promising approach for reducing the bit-cost. In this work, we demonstrate the

\* Address correspondence to simonyu@stanford.edu; hspwong@stanford.edu.

Received for review November 27, 2012 and accepted February 14, 2013.

Published online February 14, 2013 10.1021/nn305510u

© 2013 American Chemical Society

VOL.7 • NO.3 • 2320-2325 • 2013

2320

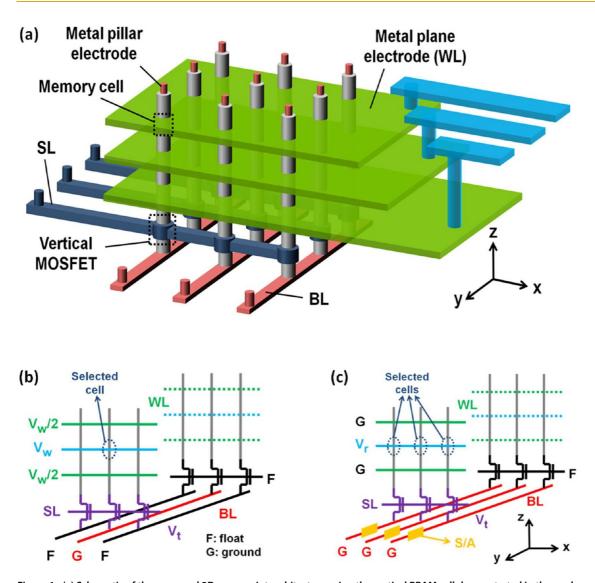

Figure 1. (a) Schematic of the proposed 3D cross-point architecture using the vertical RRAM cell demonstrated in the work. The vertical RRAM cells are formed at the intersections of each pillar electrode and each plane electrode: the resistive switching oxide layer surrounds the pillar electrode and is also in contact with the plane electrode. To enable the random access of each memory cell, three-dimensional decoding is needed through WL (decoding in the *z*-direction), BL (decoding in the *y*-direction), and SL of the gate of the vertical MOSFET (decoding in the *x*-direction). (b) Biasing diagram for the write operation. During the write operation, a specific cell is selected: write voltage (Vw) is applied on the selected cell's WL, and Vw/2 is applied on all the unselected cells' WL to avoid unintentional writing. To select the pillar where the selected cell is located, the SL of that pillar is turned on and the corresponding BL is grounded. (c) Biasing diagram for the read operation. During the read operation, arow of cells (on the same SL line) on one plane is read out simultaneously: read voltage (Vr) is applied on the selected cells' WL, the SL that controls the selected cells is turned on, and the data of a row of cells are read out by the sense amplifiers (S/A).

bit-cost-effective vertical RRAM concept in HfO<sub>x</sub>, which is one of the most explored and relatively more mature resistive switching material systems so far.<sup>9,10,24</sup> Excellent device performances are obtained in the fabricated HfO<sub>x</sub> vertical RRAM, showing the potential for 3D integration. Furthermore, we propose a 3D crosspoint architecture with three-dimensional decoding strategy (by the plane electrode word lines, by the bit lines, and by the select lines) to enable the individual cell random access, and we discuss the corresponding write/read operation schemes, both of which were not explicitly discussed in the previous works.<sup>22,23</sup>

The mechanism of the resistive switching phenomenon in oxides has been widely attributed to

YU ET AL.

the formation/rupture of the nanoscale conductive filaments, which may consist of oxygen vacancies.<sup>25</sup> The transition from high resistance state (HRS) to low resistance state (LRS) is called the SET process, while the transition from LRS to HRS is called the RESET process. The SET process is interpreted as a dielectric soft breakdown associated with the migration of oxygen ions toward one electrode, leaving behind the conductive filaments in the bulk oxide. In the bipolar RESET mode, the reserved electric field and Joule heating assist the oxygen ions' migration from the electrode/oxide interface reservoir, and they can recombine with the oxygen vacancies, thus partially rupturing the conductive filaments. For more

VOL.7 • NO.3 • 2320-2325 • 2013 A

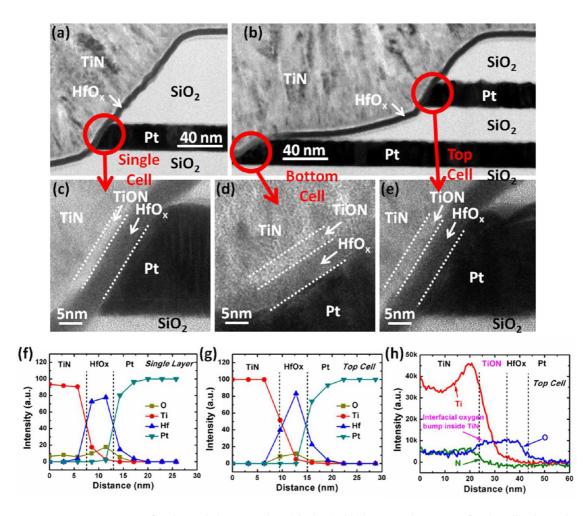

Figure 2. Cross-section TEM of (a) the single-layer sample and (b) the double-layer sample; HR-TEM of (c) the cell in the singlelayer sample, (d) the bottom cell, and (e) the top cell in the double-layer sample. The TiN pillar electrode, TiON interfacial layer, HfO<sub>x</sub> resistive switching layer, and Pt plane electrode are clearly shown. EDX composition profile through the sidewall of the cell in (f) the single-layer sample and (g) the top cell in the double-layer sample. EELS composition profile through the sidewall of (h) the top cell. Oxygen bump shows up at the TiN/HfO<sub>x</sub> interface, suggesting the formation of an interfacial TiON layer, which may cause an electron tunneling barrier and a nonlinear I-V curve for the RRAM cell.

discussions on the switching mechanism, please refer to the work in ref 26.

### **RESULTS AND DISCUSSION**

We propose a 3D cross-point memory architecture with  $4F^2/m$  cell size (F is the lithography feature size, m is the number of stacked layers), enabling the random access of individual memory cells. Figure 1a shows the schematic of our proposed structure. The vertical RRAM cells are formed at the intersections of each pillar electrode and each plane electrode (acting as the word-line, WL): the resistive switching oxide layer surrounds the pillar electrode and is also in contact with the plane electrode. To enable the random access of each memory cell individually, which is a key distinguishing feature of RRAM as compared to FLASH, three-dimensional decoding is needed. We propose using a vertical MOSFET (e.g., the gate-all-round silicon vertical nanowire transistor<sup>27</sup>) to serve as bit-line (BL) selector, whose gate is controlled by the select-line (SL). With the appropriate bias schemes on the WL

(decoding in the z-direction), BL (decoding in the y-direction), and SL (decoding in the x-direction), each memory cell in the 3D cross-point architecture can be individually accessed. The biasing diagram for the write operation is shown in Figure 1b, and that for the read operation is shown in Figure 1c. During the write operation, a specific cell is selected: write voltage (Vw) is applied on the selected cell's WL, and Vw/2 is applied on all the unselected cells' WL to avoid unintentional writing. To select the pillar where the selected cell is located, the SL of that pillar is turned on and the corresponding BL is grounded. During the read operation, a row of cells (on the same SL line) on one plane is read out simultaneously: read voltage (Vr) is applied on the selected cells' WL; SL that controls the selected cells is turned on, and the data of a row of cells are read out by the sense amplifiers.

As a proof-of-concept work, we design a bit-costeffective fabrication process for the potential 3D integration (see the Methods Section) and demonstrate a single-layer and double-layer HfOx-based vertical

Ai

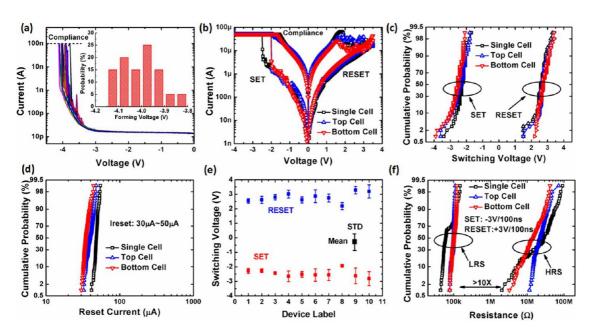

Figure 3. Statistics of the vertical HfO<sub>x</sub> RRAM's switching characteristics. (a) Forming process measured from 20 different cells (100 nA compliance is applied). Inset: Forming voltage distribution of ~4 V. (b) Direct current *I*–V bipolar switching characteristics (50  $\mu$ A compliance current is applied). (c) Switching voltage distribution (average ~3 V) by hundreds of continuous sweep cycles. (d) Reset current distribution by hundreds of continuous sweep cycles with an average of <50  $\mu$ A. (e) Switching voltage distribution collected from 10 different cells. (f) Resistance distribution obtained by hundreds of continuous pulse cycles. LRS resistance is ~100 k $\Omega$  with a HRS/LRS resistance window of >10×. Consistent switching characteristics exist among cells in the single-layer sample and top cell and bottom cell in the double-layer sample. The reasonably controlled device-to-device variation suggests the potential of stacking even more layers.

RRAM. First, the cross-sectional topology characterization of the fabricated devices is performed. Figure 2a and b show the transmission electron microscopy (TEM) image of the single-layer sample and the double-layer sample, respectively. Figure 2c-e show the high-resolution TEM (HR-TEM) image of the cell in the single-layer sample and the top cell and bottom cell in the double-layer sample. A TiN/TiON/HfO<sub>x</sub>/Pt stack is observable in the TEM image analysis. It is noted that the trench is not perfectly sharp due to the limited etching capability in our university-grade fabrication facility. Second, the materials composition characterization of the fabricated devices is performed. Figure 2f and g show the composition spatial profile through the sidewall of the single-layer sample and double-layer sample by energy-dispersive X-ray spectroscopy (EDX). The TiN pillar electrode, HfO<sub>x</sub> resistive switching layer, and Pt plane electrode are clearly shown in this spatial profile. We are also interested in the electrode/oxide interface property since it is known to affect the resistive switching behavior.<sup>28</sup> The electron energy loss spectroscopy (EELS) analysis is performed at the interface between TiN and HfO<sub>x</sub> as shown in Figure 2h: an oxygen bump appears at the interface, suggesting the formation of an interfacial TiON layer. This interfacial layer may cause an electron tunneling barrier for the RRAM device and results in a nonlinear I-V curve, as we shall see next in the device electrical characterization.

In the following, we characterize the fabricated vertical HfO<sub>x</sub> RRAM electrical properties. First, the statistics of the device performances such as the switching voltage, the reset current, and the HRS and LRS resistances are measured. Figure 3a shows the forming process for 20 different cells: the as-fabricated devices usually need  $\sim$ 4 V forming voltage to trigger the switching from the initial resistance state to LRS and initiate the subsequent switching cycles. Figure 3b shows the typical dc I-V curves of the single-layer sample and the top cell and bottom cell in the doublelayer sample. A compliance current of  $\sim$ 50  $\mu$ A is enforced by the semiconductor parameter analyzer to avoid damaging the cell during the abrupt SET process. Figure 3c shows the switching voltage distribution, which has an average of  $\sim$ 3 V. Figure 3d shows the reset current distribution with an average less than 50  $\mu$ A. Figure 3e shows the device-to-device statistics of the switching voltage from 10 different cells, showing a reasonably controlled variation and reproducibility. These statistically measured results show consistent switching characteristics among the single-layer sample and the top cell as well as the bottom cell in the double-layer sample, thus suggesting the potential of stacking multilayer vertical RRAM using this cost-effective fabrication process. Figure 3f shows the distribution of the programmed resistance value obtained by hundreds of pulse cyclings with  $\pm 3$  V/100 ns programming condition. It is seen

VOL.7 • NO.3 • 2320-2325 • 2013

JAI

www.acsnano.org

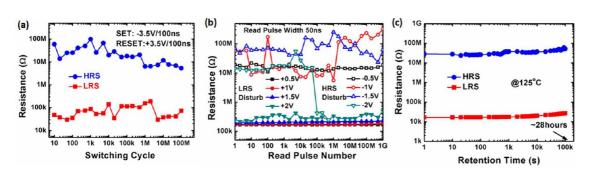

Figure 4. Reliability test of the vertical HfO<sub>x</sub> RRAM device performed on the single-layer sample. (a) Switching endurance test. The device can switch >10<sup>8</sup> cycles under  $\pm$ 3.5 V/100 ns write pulse conditions. (b) Read disturbance test. The device can maintain its states for >10<sup>9</sup> cycles under  $\pm$ 1.5 V/50 ns read pulse conditions. (c) Data retention test. The device can maintain its states for >10<sup>8</sup> s (~28 h) @ 125 °C.

that the average LRS resistance is  ${\sim}100~k\Omega,$  and the HRS/LRS resistance window maintains >10×. The measured  $\sim$ 100 k $\Omega$  LRS resistance is larger than the previously reported  $\sim 10 \text{ k}\Omega$  resistance in HfO<sub>x</sub> RRAM devices,<sup>9,12,24</sup> and the origin of this increased LRS resistance is attributed to the TiON interfacial layer, as observed in the EELS analysis in Figure 2h. This hypothesis is further supported by the LRS conduction mechanism study. The weak dependence of the LRS current on temperature (see Supporting Information S1) suggests that the conduction in LRS is dominated by electron tunneling through an interfacial barrier. As a result, the LRS resistance is effectively raised to  $\sim$ 100 k $\Omega$ . Finally, the reliability of the fabricated devices is examined. Figure 4a shows that  $>10^8$  switching endurance cycles can be achieved with  $\pm$ 3.5 V/100 ns pulse conditions. Figure 4b shows that  $>10^9$  read disturbance immunity cycles can be achieved up to  $\pm$ 1.5 V/50 ns pulse conditions. Figure 4c shows that a  $>10^5$  s data retention time can be obtained at 125 °C. The measured reliability suggests that the HfO<sub>x</sub> vertical RRAM is reliable for nonvolatile memory application.

The increased LRS resistance is beneficial for realizing the cross-point memory architecture without an explicit cell selector, because the array size is mainly limited by the ratio between the interconnect resistance and the memory LRS resistance.<sup>29</sup> A relatively large LRS resistance is helpful to reduce the voltage drop on the interconnect and mitigating the sneak path leakage current. To support this claim, we perform a SPICE simulation on the 3D cross-point architecture with the device characteristics demonstrated and the write/ read scheme proposed in this work. The simulation results suggest that an up to Mb scale array can be achievable without a cell selector. For details of the simulation, please refer to Supporting Information S2.

# CONCLUSIONS

In summary, a double-layer stacked HfO<sub>x</sub> vertical RRAM has been demonstrated using a bit-costeffective fabrication process for the 3D integration. Excellent and consistent switching characteristics of the fabricated devices suggest the potential of stacking even more layers. A TiON interfacial layer is introduced for obtaining nonlinear I-V curves. As a result, the LRS resistance gets increased at low applied bias for the unselected cells in an array, which is beneficial for a cross-point array without an explicit cell selector. This work paves a technology path toward a 3D cross-point memory architecture with the emerging oxide-based RRAM devices. Future research directions include finding appropriate electrode materials that can replace Pt since Pt is not fully compatible with the CMOS integration process.

#### **METHODS**

**Device Fabrication.** We design a bit-cost-effective fabrication process for potential 3D integration, and the schematic of the process flow is shown in Supporting Information S3: (1) Multi-layer stacked Pt (20 nm)/SiO<sub>2</sub> (30 nm) is deposited by e-beam evaporation and low-pressure chemical vapor deposition, respectively; (2) a trench (1 – 100  $\mu$ m in size) is dry etched down to the bottom SiO<sub>2</sub> layer; (3) 5 nm HfO<sub>x</sub> is deposited by atomic layer deposition, which conformally covers the sidewall of the trench; (4) 150 nm TiN is deposited by reactive sputtering to fill the trench as the pillar electrode; the oxygen ambient is introduced during sputtering to form the TiON interfacial layer; (5) the Pt plane electrode at the edge of the memory cell area is exposed by dry etching so it can be separately contacted electrically. The vertical HfO<sub>x</sub> RRAM cells are formed at the sidewall between

YU ET AL.

the TiN pillar electrode and Pt plane electrode. Two types of samples have been fabricated: one is the single-layer sample with one cell on the sidewall per trench; the other is the double-layer sample with two cells on the sidewall per trench.

TEM and Composition Characterization. The TEM-ready samples were prepared using the *in situ* focused ion beam (FIB) lift out technique on an FEI 830 dual beam FIB/SEM. The sample was coated with a protective platinum layer prior to FIB milling. The samples were imaged with a FEI Tecnai TF-20 FEG/TEM operated at 200 kV in bright-field mode, high-resolution mode, and high-angle annular dark-field STEM mode. EDX spectra were obtained in STEM mode using a nominal 3 nm electron beam and an Oxford INCA EDX detector system. The EELS line scan was obtained in STEM mode using a nominal 1 nm electron beam and a Gatan Enfina DigiP EELS spectrometer.

VOL.7 • NO.3 • 2320-2325 • 2013

**Electrical Measurements.** Electrical measurements are performed using a Keithley 4200 semiconductor parameter analyzer and an Agilent 81150A pulse generator. The voltage is applied on the Pt plane electrode, and the TiN pillar electrode is grounded as a reference.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. We thank C.-Y. Chen and S. Gupta of Stanford University for the discussions on device fabrication, and we thank P. Huang and Y. Deng of Peking University for the simulation of the 3D cross-point array. This work is supported in part by the member companies of the Stanford Non-Volatile Memory Technology Research Initiative (NMTRI) and the 973 Program (2011CBA00602) of China. This work was done in part at the Stanford Nanofabrication Facility (SNF), a member of the NSF-supported National Nanotechnology Infrastructure Network (NNIN). B.G. is supported in part by the Stanford School of Engineering China Research Exchange Program. S.Y. is additionally supported by the Stanford Graduate Fellowship.

Supporting Information Available: This section includes the conduction mechanism study of the LRS, the 3D cross-point memory array simulation, and the bit-cost-effective fabrication process for potential 3D integration. This material is available free of charge via the Internet at http://pubs.acs.org.

## **REFERENCES AND NOTES**

- Waser, R.; Dittmann, R.; Staikov, G.; Szot, K. Redox-Based Resistive Switching Memories–Nanoionic Mechanisms, Prospects, and Challenges. *Adv. Mater.* 2009, *21*, 2632–2663.

- Wong, H.-S. P.; Lee, H.-Y.; Yu, S.; Chen, Y.-S.; Wu, Y.; Chen, P.-S.; Lee, B.; Chen, F. T.; Tsai, M.-J. Metal Oxide RRAM. *Proc. IEEE* 2012, 100, 1951–1970.

- Jo, S. H.; Kim, K.-H.; Lu, W. Programmable Resistance Switching in Nanoscale Two-Terminal Devices. *Nano Lett.* 2009, 9, 496–500.

- Chai, Y.; Wu, Y.; Takei, K.; Chen, H.-Y.; Yu, S.; Chan, P. C. H.; Javey, A.; Wong, H.-S. P. Nanoscale Bipolar and Complementary Resistive Switching Memory Based on Amorphous Carbon. *IEEE Trans. Electron Devices* **2011**, *58*, 3933–3939.

- Jang, J.; Pan, F.; Braam, K.; Subramanian, V. Resistance Switching Characteristics of Solid Electrolyte Chalcogenide Ag<sub>2</sub>Se Nanoparticles for Flexible Nonvolatile Memory Applications. *Adv. Mater.* **2012**, *24*, 3573–3576.

- Lee, M. J.; Han, S.; Jeon, S. H.; Park, B. H.; Kang, B. S.; Ahn, S. E.; Kim, K. H.; Lee, C. B.; Kim, C. J.; Yoo, I. K.; *et al.* Electrical Manipulation of Nanofilaments in Transition-Metal Oxides for Resistance-Based Memory. *Nano Lett.* **2009**, *9*, 1476–1481.

- Yang, J. J.; Pickett, M. D.; Li, X.; Ohlberg, D.; Stewart, D.; Williams, R. S. Memristive Switching Mechanism for Metal/ Oxide/Metal Nanodevices. *Nat. Nanotechnol.* 2008, *3*, 429–433.

- Chien, W.-C.; Lee, M.-H.; Lee, F.-M.; Lin, Y.-Y.; Lung, H.-L.; Hsieh, K.-Y.; Lu, C.-Y. A Multi-Level 40nm WOx Resistive Memory with Excellent Reliability. *IEEE Tech. Dig. IEDM* 2011, 725–728.

- Lee, H. Y.; Chen, Y. S.; Chen, P. S.; Gu, P. Y.; Hsu, Y. Y.; Wang, S. M.; Liu, W. H.; Tsai, C. H.; Sheu, S. S.; Chiang, P. C.; *et al.* Evidence and Solution of Over-RESET Problem for HfOx Based Resistive Memory with Sub-ns Switching Speed and High Endurance. *IEEE Tech. Dig. IEDM* **2010**, 460–463.

- Govoreanu, B.; Kar, G. S.; Chen, Y.-Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Radu, I. P.; Goux, L.; Clima, S.; Degraeve, R.; *et al.* 10 × 10nm<sup>2</sup> Hf/HfOx Crossbar Resistive RAM with Excellent Performance, Reliability and Low-Energy Operation. *IEEE Tech. Dig. IEDM* **2011**, 729–732.

- Lee, M.-J.; Lee, C. B.; Lee, D.; Lee, S. R.; Chang, M.; Hur, J. H.; Kim, Y.-B.; Kim, C.-J.; Seo, D. H.; Seo, S.; *et al.* A Fast, High-Endurance and Scalable Non-volatile Memory Device Made from Asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> Bilayer Structures. *Nat. Mater.* **2011**, *10*, 625–630.

- 12. Kim, W.; Park, S. I.; Zhang, Z.; Yang-Liauw, Y.; Sekar, D.; Wong, H.-S. P.; Wong, S. Forming-Free Nitrogen-Doped

AlOx RRAM with Sub-µA Programming Current. *Tech. Dig. Symp. VLSI Technol.* **2011**, 22–23.

- Sheu, S.-S.; Chang, M.-F.; Lin, K.-F.; Wu, C.-W.; Chen, Y.-S.; Chiu, P.-F.; Kuo, C.-C.; Yang, Y.-S.; Chiang, P.-C.; Lin, W.-P.; et al. A 4Mb Embedded SLC Resistive-RAM Macro with 7.2ns Read-Write Random-Access Time and 160ns MLC-Access Capability. *IEEE Tech. Dig. ISSCC* 2011, 200–202.

- Yu, S.; Guan, X.; Wong, H.-S. P. On the Switching Parameter Variation of Metal Oxide RRAM - Part II: Model Corroboration and Device Design Strategy. *IEEE Trans. Electron Devices* 2012, 59, 1183–1189.

- 15. Goda, A.; Parat, K. Scaling Directions for 2D and 3D NAND Cells. *IEEE Tech. Dig. IEDM* **2012**, 13–16.

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; *et al.* Bit Cost Scalable Technology with Punch and Plug Process for Ultra High Density Flash Memory. *Tech. Dig. Symp. VLSI Technol.* **2007**, 14–15.

- Kim, W.; Choi, S.; Sung, J.; Lee, T.; Park, C.; Ko, H.; Jung, J.; Yoo, I.; Park, Y. Multi-Layered Vertical Gate NAND Flash Overcoming Stacking Limit for Terabit Density Storage. *Tech. Dig. Symp. VLSI Technol.* **2009**, 188–199.

- Jang, J.; Kim, H.-S.; Cho, W.; Cho, H.; Kim, J.; Shim, S. I.; Jang, Y.; Jeong, J.-H.; Son, B.-K.; Kim, D. W.; et al. Vertical Cell Array Using TCAT (Terabit Cell Array Transistor) Technology for Ultra High Density NAND Flash Memory. Tech. Dig. Symp. VLSI Technol. 2009, 192–193.

- Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; Matsunami, J.; Fujiwara, T.; Nagata, Y.; et al. Pipe-Shaped BiCS Flash Memory with 16 Stacked Layers and Multi-Level-Cell Operation for Ultra High Density Storage Devices. Tech. Dig. Symp. VLSI Technol. 2009, 136–137.

- Lee, M.-J.; Kim, S. I.; Lee, C. B.; Yin, H.; Ahn, S.-E.; Kang, B. S.; Kim, K. H.; Park, J. C.; Kim, C. J.; Song, I.; *et al.* Low-Temperature-Grown Transition Metal Oxide Based Storage Materials and Oxide Transistors for High-Density Nonvolatile Memory. *Adv. Funct. Mater.* **2009**, *19*, 1587–1593.

- Kim, K.-H.; Gaba, S.; Wheeler, D.; Cruz-Albrecht, J. M.; Hussain, T.; Srinivasa, N.; Lu, W. A Functional Hybrid Memristor Crossbar-Array CMOS System for Data Storage and Neuromorphic Applications. *Nano Lett.* **2012**, *12*, 389–395.

- Baek, I. G.; Park, C. J.; Ju, H.; Seong, D. J.; Ahn, H. S.; Kim, J. H.; Yang, M. K; Song, S. H.; Kim, E. M; Park, S. O.; *et al.* Realization of Vertical Resistive Memory (VRRAM) Using Cost Effective 3D Process. *IEEE Tech. Dig. IEDM* **2011**, 737– 740.

- Chien, W. C.; Lee, F. M.; Lin, Y. Y.; Lee, H. M.; Chen, S. H.; Hsieh, C. C.; Lai, E. K.; Hui, H. H.; Huang, Y. K.; Yu, C. C.; *et al.* Multi-Layer Sidewall WOX Resistive Memory Suitable for 3D ReRAM. *Tech. Dig. Symp. VLSI Technol.* **2012**, 153–154.

- Yu, S.; Wu, Y.; Wong, H.-S. P. Investigating the Switching Dynamics and Multilevel Capability of Bipolar Metal Oxide Resistive Switching Memory. *Appl. Phys. Lett.* **2011**, *98*, 103514.

- Kwon, D.-H.; Kim, K.; Jang, J.; Jeon, J.; Lee, M.; Kim, G.; Li, X.-S.; Park, G.-S.; Lee, B.; Han, S.; *et al.* Atomic Structure of Conducting Nanofilaments in TiO<sub>2</sub> Resistive Switching Memory. *Nat. Nanotechnol.* **2010**, *5*, 148–153.

- Guan, X.; Yu, S.; Wong, H.-S. P. On the Switching Parameter Variation of Metal Oxide RRAM - Part I: Physical Modeling and Simulation Methodology. *IEEE Trans. Electron Devices* 2012, 59, 1172–1182.

- Singh, N.; Buddharaju, K. D.; Manhas, S. K.; Agarwal, A.; Rustagi, S. C.; Lo, G. Q.; Balasubramanian, N.; Kwong, D.-L. Si, SiGe Nanowire Devices by Top-Down Technology and Their Applications. *IEEE Trans. Electron Devices* **2008**, *55*, 3107–3118.

- Yu, S.; Wong, H.-S. P. A Phenomenological Model for the Reset Mechanism of Metal Oxide RRAM. *IEEE Electron Device Lett.* 2010, *31*, 1455–1457.

- Liang, J.; Wong, H.-S. P. Cross-Point Memory Array without Cell Selectors—Device Characteristics and Data Storage Pattern Dependencies. *IEEE Trans. Electron Devices* 2010, 57, 2531–2538.

www.acsnano.org